# Tiny Machine Learning: Progress and Futures

Ji Lin Ligeng Zhu Wei-Ming Chen Wei-Chen Wang Song Han

Massachusetts Institute of Technology

https://tinyml.mit.edu

Abstract—Tiny Machine Learning (TinyML) is a new frontier of machine learning. By squeezing deep learning models into billions of IoT devices and microcontrollers (MCUs), we expand the scope of AI applications and enable ubiquitous intelligence. However, TinyML is challenging due to hardware constraints: the tiny memory resource makes it difficult to hold deep learning models designed for cloud and mobile platforms. There is also limited compiler and inference engine support for bare-metal devices. Therefore, we need to co-design the algorithm and system stack to enable TinyML. In this review, we will first discuss the definition, challenges, and applications of TinyML. We then survey the recent progress in TinyML and deep learning on MCUs. Next, we will introduce MCUNet, showing how we can achieve ImageNet-scale AI applications on IoT devices with system-algorithm co-design. We will further extend the solution from inference to training and introduce tiny on-device training techniques. Finally, we present future directions in this area. Today's "large" model might be tomorrow's "tiny" model. The scope of TinyML should evolve and adapt over time.

# *Index Terms*—TinyML, Efficient Deep Learning, On-Device Training, Learning on the Edge

## I. OVERVIEW OF TINY MACHINE LEARNING

Machine learning (ML) has made significant impacts on various fields, including vision, language, and audio. However, state-of-the-art models often come at the cost of high computation and memory, making them expensive to deploy. To address this, researchers have been working on efficient algorithms, systems, and hardware to reduce the cost of machine learning models in various deployment scenarios. There are two main subdomains of efficient ML: EdgeML and CloudML (Figure 1). While CloudML focuses on improving latency and throughput on cloud servers, EdgeML focuses on improving energy efficiency, latency, and privacy on edge devices. These two domains also intersect in areas such as hybrid inference [1, 2], over-the-air (OTA) updates, and federated learning between the edge and cloud [3]. In recent years, there has been significant progress in extending the scope of EdgeML to ultra-low-power devices such as IoT devices and microcontrollers, known as TinyML.

TinyML has several key advantages. It enables machine learning using only a few hundred kilobytes of memory which greatly reduces the cost. With billions of IoT devices producing more and more data in our daily lives, there is a growing need for low-power, always-on, on-device AI. By performing on-device inference near the sensor, TinyML enables better

**Fig. 1.** Efficiency is critical for CloudML, EdgeML, and TinyML. CloudML targets high-throughput accelerators like GPUs, while EdgeML focuses on portable devices like mobile phones. TinyML further pushes the efficiency boundary, enabling powerful ML models to run on ultra-low-power devices such as microcontrollers.

responsiveness and privacy while reducing the energy cost associated with wireless communication. On-device processing of data can be beneficial for applications where real-time decision-making is crucial, such as autonomous vehicles.

In addition to inference, we push the frontier of TinyML to enable on-device training on IoT devices. Itrevolutionizes EdgeAI through continuous and lifelong learning. Edge device can finetune the model on itself rather than transmitting data to cloud servers, which protects privacy. On-device learning has numerous benefits and a variety of applications. For example, home cameras can continuously recognize new faces, and email clients can gradually improve their prediction by updating customized language models. It also enables IoT applications that do not have a physical connection to the internet to adapt to the environment, such as precision agriculture and ocean sensing.

In this review, we will first discuss the definition and challenges of TinyML, analyzing why we can't directly scale mobile ML or cloud ML models for tinyML. Then we delve into the importance of system-algorithm co-design in TinyML. We will then survey recent literature and the progress of the field, presenting a holistic survey and comparison in Tables II and III. Next, we will introduce our TinyML project, MCUNet, which combines efficient system and algorithm design to enable TinyML for both inference to training. Finally, we will discuss several emerging topics for future research directions in the field.

## A. Challenges of TinyML

The success of deep learning models often comes at the cost of high computation, which is not feasible for use in TinyML applications due to the strict resource constraints of devices such as microcontrollers. Deploying and training AI models on MCU is extremely hard: No DRAM, no operating systems (OS), and strict memory constraints (SRAM is smaller than 256kB, and FLASH is read-only). The available resources on these devices are orders of magnitude smaller than those

This paper is published by IEEE Circuits and Systems Magazine. © 2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

**TABLE I. Left**: Microcontrollers have 3 orders of magnitude *less* memory and storage compared to mobile phones, and 5-6 orders of magnitude less than cloud GPUs. The extremely limited memory makes deep learning deployment difficult. **Right**: The peak memory and storage usage of widely used deep learning models. ResNet-50 exceeds the resource limit on microcontrollers by  $100 \times$ , MobileNet-V2 exceeds by  $20 \times$ . Even the int8 quantized MobileNetV2 requires  $5.3 \times$  larger memory and can't fit a microcontroller.

|         | <b>Cloud AI</b><br>(NVIDIA V10 | )() <b>→</b> | <b>Mobile AI</b> (iPhone 11) |        | Tiny AI<br>(STM32F746 | )     | ResNet-50 | MobileNetV2 | MobileNetV2<br>(int8) |

|---------|--------------------------------|--------------|------------------------------|--------|-----------------------|-------|-----------|-------------|-----------------------|

| Memory  | 16 GB                          | 4×           | → 4 GB                       | 3100×  | 320 kB                | ← gaj | p→ 7.2 MB | 6.8 MB      | 1.7 MB                |

| Storage | TB~PB                          | 1000×        | → >64 GB                     | 64000× | 1 MB                  | ← gaj | p→ 102MB  | 13.6 MB     | 3.4 MB                |

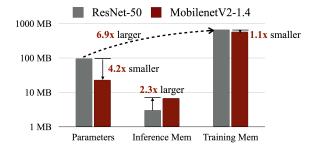

**Fig. 2.** We can't directly scale mobile ML or cloud ML models for TinyML. MobilenetV2 [4] with a width of 1.4 was used for the experiments. The batch size was set to 1 for inference and 8 for training. While MobilenetV2 reduces the number of parameters by  $4.2 \times$  compared to ResNet, the peak memory usage increases by  $2.3 \times$  for inference and only improves by  $1.1 \times$  for training. Additionally, the total required training memory is  $6.9 \times$  larger than the memory needed for inference. These results demonstrate the significant memory bottleneck for TinyML, and the bottleneck is the activation memory, not the number of parameters.

available on mobile platforms (see Table I). Previous work in the field has either (I) focused on reducing model parameters without addressing the real bottleneck of activations, or (II) only optimized operator kernels without considering improving the network architecture design. Neither of which considers the problem from a co-design perspective, and this has led to less optimal solutions for TinyML applications. We observe several unique challenges of TinyML and postulate how they might be overcome:

## 1) Models designed for mobile platforms does not fit TinyML

There has been a lot of effort optimizing deep learning models for mobile platforms like MobileNets [5, 4] and ShuffleNet [6]. However, since mobile devices have sufficient memory resources (Table I), the model designs focus on parameters/FLOPs/latency reduction but not peak memory usage. As shown in Figure 2 Left and Middle, comparing two models with the same level of ImageNet accuracy, MobileNetV2-1.4 has  $4.2 \times$  smaller model size compared to ResNet-50, but its peak memory even larger by  $2.3 \times$ . Using MobileNet designs does not adequately address the SRAM limit, instead, it actually makes the situation even worse compared to ResNet. Therefore, we need to rethink the model design principles for TinyML.

# 2) Directly adapting models for inference does not work for tiny training.

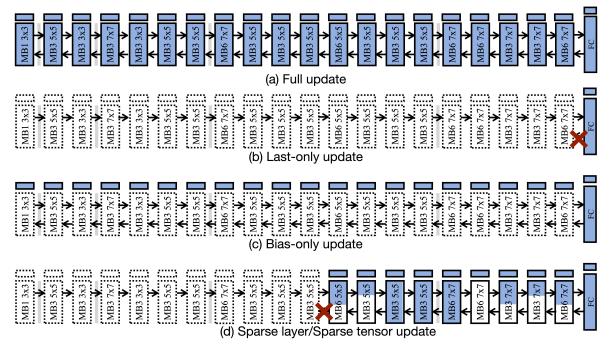

Training poses an even greater challenge in terms of resource constraints, as intermediate activations must be stored in order to compute backward gradients. When moving from inference to training with full backpropagation, the required memory increases by a factor of 6.9. As shown in Figure 2, the training memory requirements of MobileNets are not much better than ResNets (improved by only 10%). Tiny IoT devices such as microcontrollers typically have a limited SRAM size, such as 256KB, which is barely enough for the inference of deep learning models, let alone training. Previous work in the cloud and mobile AI has focused on reducing FLOPs [5, 4, 7] or only optimizing inference memory [8, 9]. However, even using memory-efficient inference models such as MCUNet [8] to bridge the three orders of magnitude gap, training is still too expensive for tiny platforms. If we follow conventional full model update schemes, the model must be scaled down significantly to fit within the tight memory constraints, resulting in low accuracy. This highlights the need to redesign backpropagation schemes and investigate new learning algorithms to reduce the main activation memory bottleneck and enable fast and accurate training on tiny devices. In Section IV, we will discuss this issue in detail and introduce the concept of sparse layer and sparse tensor updates.

#### 3) Co-design is necessary for TinyML

Co-design is necessary for TinyML because it allows us to fully customize the solutions that are optimized for the unique constraints of tiny devices. Previous neural architectures like MobileNets [5, 4], and ResNets [10] are designed for mobile/cloud scenarios but not well-suited for tiny hardware. Therefore, we need to design neural architectures that are suitable for TinyML applications. On the other hand, existing deep training frameworks are optimized for cloud servers and lack support for memory-efficient forward and backward, thus cannot fit into tiny devices. The huge gap (>1000×) between the resources of tiny IoT devices and the requirements of current frameworks prohibits the usage. To address these challenges, it is necessary to develop algorithms, systems, and training techniques that are specifically tailored to the settings of these tiny platforms.

## B. Applications of TinyML

By democratizing costly deep learning models to IoT devices, TinyML has many practical applications. Some example applications include:

Personalized healthcare: TinyML can allow wearable devices, such as smartwatches, to continuously track the activities and oxygen saturation status of the user in order to provide health suggestions [11, 12, 13, 14]. Body pose estimation is also a crucial application for elderly healthcare [15].

- Wearable applications: TinyML can assist people with wearable or IoT devices for speech applications, *e.g.*, keyword spotting, automatic speech recognition, and speaker verification [16, 17, 18].

- Smart home: TinyML can enable object detection, image recognition, and face detection on IoT devices to build smart environments, such as smart homes and hospitals [19, 20, 21, 22, 23].

- Human-machine interface: TinyML can enable humanmachine interface applications, like hand gesture recognition [24, 25, 26, 27]. TinyML is also capable of predicting and recognizing sign languages [28].

- Smart vehicle and transportation: TinyML can perform object detection, lane detection, and decision making without a cloud connection, achieving high-accuracy and low-latency results for autonomous driving scenarios [29, 30, 31].

- Anomaly detection: TinyML can equip robots and sensors with the capability to perform anomaly detection to reduce human efforts [32, 33, 34].

- Ecology and agriculture: TinyML can also help with ecological, agricultural, environmental, and phenomics applications so as to conserve endangered species or forecast weather activities [35, 36, 37, 38, 39, 40].

Overall, the potential applications of TinyML are diverse and numerous, and will expand as the field continues to advance.

## II. RECENT PROGRESS IN TINYML

# A. Recent Progress on TinyML Inference

TinyML and deep learning on MCUs have seen rapid growth in industry and academia in recent years. The primary challenge of deploying deep learning models on MCUs for inference is the limited memory and computation available on these devices. For example, a popular ARM Cortex-M7 MCU, the STM32F746, has only 320KB of SRAM and 1MB of flash memory. In deep learning scenarios, SRAM limits the size of activations (read and write) while flash memory limits the size of the model (read-only). In addition, the STM32F746 has a processor with a clock speed of 216 MHz, which is 10 to 20 times lower than laptops. To enable deep learning inference on MCUs, researchers have proposed various designs and solutions to address these issues. Table II summarizes the recent related studies on TinyML targeting MCUs, including both algorithm solutions and system solutions. In Table III, we measured three different metrics (i.e., latency, peak memory, and flash usage) of four representative related studies (i.e., CMSIS-NN [41], X-Cube-AI [42], TinyEngine [8], and TF-Lite Micro [47]) on an identical MCU (STM32H743) and identical datasets (VWW and Imagenet), in order to provide a more accurate and transparent comparison.

## a) Algorithm Solutions

The importance of neural network's efficiency to the overall performance of a deep learning system cannot be overstated. Compressing off-the-shelf networks by removing redundancy and reducing complexity through pruning [57, 58, 59, 60, 61, 62] and quantization [63, 64, 65, 66, 67, 68, 69, 70] are two popular methods to improve network efficiency. Tensor decomposition [71, 72, 73] is also an efficient compression technique. In order to enhance network efficiency, knowledge distillation is also a method to transfer information learned from one teacher model to another student model [74, 75, 76, 77, 78, 79, 80, 81]. Another method is to directly design tiny and efficient network structures [5, 4, 6, 7]. Recently, neural architecture search (NAS) has dominated the design of efficient networks [82, 83, 84, 85, 86, 87].

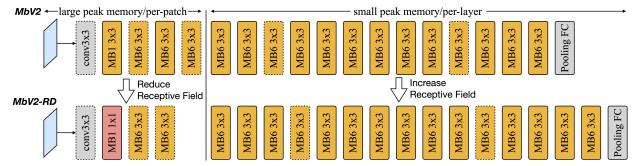

To make deep learning feasible on MCUs, researchers have proposed various algorithm solutions. Rusci et al. proposed a rule-based quantization strategy that minimizes the bit precision of activations and weights in order to reduce memory usage [45]. Depending on the memory constraints of various devices, this method can quantize activations and weights with 8 bits, 4 bits, or 2 bits of mixed precision. On the other hand, although neural architecture search (NAS) has been successful in finding efficient network architectures, its effectiveness is highly dependent on the quality of the search space [88]. For MCUs with limited memory, standard model designs and appropriate search spaces are especially lacking. To address this, TinyNAS, proposed as part of MCUNet, employs a twostep NAS strategy that optimizes the search space according to the available resources [8]. TinyNAS then specializes network architectures within the optimized search space, allowing it to automatically deal with a variety of constraints (e.g., device, latency, energy, memory) at low search costs. MicroNets observed that the inference latency of networks in the NAS search space for MCUs varies linearly with the number of FLOPs in the model [48]. As a result, it proposed differentiated NAS, which treats the FLOPs as a proxy for latency in order to achieve both low memory consumption and high speed. MCUNetV2 identified that the imbalanced memory distribution is the primary memory bottleneck in most convolutional neural network designs, where the memory usage of the first few blocks is an order of magnitude greater than the rest of the network [9]. As a result, this study proposed receptive field redistribution to shift the receptive field and FLOPs to a later stage, reducing the halo's computation overhead. To minimize the difficulty of manually redistributing the receptive field, this study also automated the neural architecture search process to simultaneously optimize the neural architecture and inference scheduling. UDC explored a broader design search space to generate compressible neural networks with high accuracy for neural processing units (NPUs), which can address the memory problem by exploiting model compression with a broader range of weight quantization and sparsity [51].

## b) System Solutions

In recent years, popular training frameworks such as Py-Torch [89], TensorFlow [90], MXNet [91], and JAX [92] have contributed to the success of deep learning. However, these frameworks typically rely on a host language (*e.g.*, Python) and various runtime systems, which adds significant overhead and makes them incompatible with tiny edge devices. Emerging frameworks such as TVM [93], TF-Lite [94], MNN [95], NCNN [96], TensorRT [97], and OpenVino [98]

|                                    | CMSIS-NN<br>arXiv'18 [41]  | X-Cube-AI<br>[42]              | MicroTVM<br>[43]           | Liberis et al.<br>MLSys'20 [44] | Rusci et al.<br>MLSys'20 [45] | CMix-NN<br>TCAS'20 [46]     |

|------------------------------------|----------------------------|--------------------------------|----------------------------|---------------------------------|-------------------------------|-----------------------------|

| On-Device Training<br>or Inference | Inference                  | Inference                      | Inference                  | Inference                       | Inference                     | Inference                   |

| Measured Device                    | MCU<br>(STM32H743)         | MCU<br>(STM32H743)             | MCU<br>(STM32F746)         | MCU<br>(STM32F767)              | MCU<br>(STM32H743)            | MCU<br>(STM32H743)          |

| Dataset                            | ImageNet                   | ImageNet                       | CIFAR-10 VWW               |                                 | ImageNet                      | ImageNet                    |

| Model                              | MobileNetV1                | MobileNetV1                    | SmallCifar                 | MobileNetV1                     | MobileNetV1                   | MobileNetV1                 |

| Input Resolution                   | 192                        | 192                            | 32                         | 96                              | 224                           | 192                         |

| Width Multiplier                   | 0.5                        | 0.5                            | 1.0                        | 0.25                            | 0.75                          | 0.5                         |

| Data Bitwidth                      | INT8                       | INT8                           | INT8                       | INT8                            | Mixed                         | INT8                        |

| Latency                            | 510 ms <sup>1</sup>        | $437 \text{ ms}^1$             | $157 \text{ ms}^3$         | 1325 ms                         | 1860 ms                       | 677 ms                      |

| Peak Memory                        | < 1 MB <sup>2</sup>        | $< 1 \text{ MB}^2$             | 144 KB <sup>3</sup>        | 55 KB                           | $< 512 \text{ KB}^2$          | $< 512 \text{ KB}^2$        |

| Flash Usage                        | $1.4 \text{ MB}^1$         | $1.4 \text{ MB}^1$             | $< 1 \text{ MB}^2$         | $< 2 \text{ MB}^2$              | 2 MB                          | 1.4 MB                      |

| Energy Consumption                 | $135 \text{ mJ}^1$         | $115 \text{ mJ}^1$             | -                          | 735 mJ                          | $491 \text{ mJ}^4$            | $179 \text{ mJ}^4$          |

| Top-1 Accuracy                     | $59.5\%^{1}$               | $59.5\%^{1}$                   | -                          | $\sim 76\%$                     | 68.2%                         | 62.9%                       |

|                                    | MCUNetV1<br>NeurIPS'20 [8] | TF-Lite Micro<br>MLSys'21 [47] | MicroNets<br>MLSys'21 [48] | MCUNetV2<br>NeurIPS'21 [9]      | TinyOps<br>CVPRW'22 [49]      | TinyMaix<br>[50]            |

| On-Device Training<br>or Inference | Inference                  | Inference                      | Inference                  | Inference                       | Inference                     | Inference                   |

| Measured Device                    | MCU<br>(STM32H743)         | MCU<br>(STM32F746)             | MCU<br>(STM32F746)         | MCU<br>(STM32H743)              | MCU<br>(STM32F746)            | MCU<br>(STM32H750)          |

| Dataset                            | ImageNet                   | ImageNet                       | VWW                        | ImageNet                        | ImageNet                      | VWW                         |

| Model                              | MCUNet                     | MobileNetV2                    | MicroNet-<br>VWW-1         | MCUNet                          | MNASNet                       | MobileNetV1                 |

| Input Resolution                   | 160                        | 64                             | 160                        | 224                             | 96                            | 96                          |

| Width Multiplier                   | N/A                        | 0.35                           | N/A                        | N/A                             | 1.0                           | 0.25                        |

| Data Bitwidth                      | INT8                       | INT8                           | INT8                       | INT8                            | INT8                          | Mixed                       |

| Latency                            | 463 ms                     | 296 ms <sup>3</sup>            | 1133 ms                    | 859 ms                          | 866 ms                        | 64 ms                       |

| Peak Memory                        | 416 KB                     | 211 KB <sup>3</sup>            | 285 KB                     | 434 KB                          | 397 KB                        | 54 KB                       |

| Flash Usage                        | 1.7 MB                     | $< 1 \text{ MB}^2$             | 0.8 MB                     | 1.8 MB                          | 4.7 MB                        | 0.2 MB                      |

| Energy Consumption                 | -                          | -                              | 479 mJ                     | -                               | 546 mJ                        | -                           |

| Top-1 Accuracy                     | 68.0%                      | -                              | 88.0%                      | 71.8%                           | 64.0%                         | $\sim 76\%$                 |

|                                    | UDC<br>NeurIPS'22 [51]     | TinyTL<br>NeurIPS'20 [52]      | TinyOL<br>IJCNN'21 [53]    | POET<br>ICML'22 [54]            | MiniLearn<br>EWSN'22 [55]     | MCUNetV3<br>NeurIPS'22 [56] |

| On-Device Training<br>or Inference | Inference                  | Training                       | Training                   | Training                        | Training                      | Training                    |

| Measured Device                    | N/A<br>(Simulation)        | N/A<br>(Simulation)            | MCU<br>(nRF52840)          | MCU<br>(nRF52840)               | MCU<br>(nRF52840)             | MCU<br>(STM32F746)          |

| Dataset                            | ImageNet                   | CIFAR-10                       | Self-Collected             | CIFAR-10                        | KWS-subset                    | VWW                         |

| Model                              | UDC                        | ProxylessNAS-<br>Mobile        | Autoencoder                | ResNet-18                       | Customized                    | MCUNet                      |

| Data Bitwidth                      | Mixed                      | FP32                           | FP32                       | FP32                            | Mixed                         | INT8                        |

| Latency                            | -                          | -                              | -                          | 49 ms                           | 93 ms                         | 546 ms                      |

| Peak Memory                        | -                          | 65 MB                          | $< 256 \text{ KB}^2$       | 271 KB                          | 196 KB                        | 173 KB                      |

| Flash Usage                        | 1.27 MB                    | -                              | $< 1 \text{ MB}^2$         | $< 1 \text{ MB}^2$              | 0.9 MB                        | 0.7MB                       |

| Energy Consumption                 | -                          | -                              | -                          | 868 mJ                          | 1486 mJ                       | -                           |

| Top-1 Accuracy                     | 72.1%                      | 96.1%                          | -                          | 95.5%                           | 88.5%                         | 89.3%                       |

TABLE II. Specification and performance comparison of recent progress on TinyML research targeting microcontrollers.

<sup>1</sup>Measured by CMix-NN paper [46]. <sup>2</sup>Speculated by the specification of the corresponding MCU. <sup>3</sup>Measured by MCUNet paper [8]. <sup>4</sup>In a private email on Dec. 22, 2022, the authors of the papers replied that the energy consumption should be interpreted as mJ instead of  $\mu$ J in their papers.

offer lightweight runtime systems for edge devices such as mobile phones, but they are not yet small enough for MCUs.

|                              | CMSIS-NN<br>arXiv'18 [41]  | X-Cube-AI<br>[42]           | TinyEngine<br>NeurIPS'20 [8] | TF-Lite Micro<br>MLSys'21 [47] |

|------------------------------|----------------------------|-----------------------------|------------------------------|--------------------------------|

| Dataset:                     | VWW; Model: mcunet-vww0    | ; Input Resolution: 64; W   | idth Multiplier: N/A; Top-1  | Accuracy: 87.3%                |

| Latency                      | 53 ms                      | 32 ms                       | 27 ms                        | 587 ms                         |

| Peak Memory                  | 163 KB                     | 88 KB                       | 59 KB                        | 163 KB                         |

| Storage usage                | 646 KB                     | 463 KB                      | 453 KB                       | 627 KB                         |

| Dataset:                     | VWW; Model: mcunet-vww1    | ; Input Resolution: 80; W   | idth Multiplier: N/A; Top-1  | Accuracy: 88.9%                |

| Latency                      | 97 ms                      | 57 ms                       | 51 ms                        | 1120 ms                        |

| Peak Memory                  | 220 KB                     | 113 KB                      | 92 KB                        | 220 KB                         |

| Storage usage                | 736 KB                     | 534 KB                      | 521 KB                       | 718 KB                         |

| Dataset: V                   | /WW; Model: mcunet-vww2    | ; Input Resolution: 144; W  | idth Multiplier: N/A; Top-1  | Accuracy: 91.8%                |

| Latency                      | 478 ms                     | 269 ms                      | 234 ms                       | 5310 ms                        |

| Peak Memory                  | 390 KB                     | 201 KB                      | 174 KB                       | 385 KB                         |

| Storage usage                | 1034 KB                    | 774 KB                      | 741 KB                       | 1016 KB                        |

| Dataset:                     | mageNet: Model: mcunet-in0 | : Input Resolution: 48: W   | idth Multiplier: N/A; Top-1  | Accuracy: 40.4%                |

|                              | 51 ms                      | 35 ms                       | 25 ms                        | 596 ms                         |

|                              |                            |                             |                              | 161 KB                         |

| Peak Memory                  | 161 KB                     | 69 KB                       | 49 KB                        |                                |

| Storage usage                | 1090 KB                    | 856 KB                      | 842 KB                       | 1072 KB                        |

| Dataset: ]                   | mageNet; Model: mcunet-in1 | ; Input Resolution: 96; W   | idth Multiplier: N/A; Top-1  | Accuracy: 49.9%                |

| Latency                      | 103 ms                     | 63 ms                       | 56 ms                        | 1227 ms                        |

| Peak Memory                  | 219 KB                     | 106 KB                      | 96 KB                        | 219 KB                         |

| Storage usage                | 956 KB                     | 737 KB                      | 727 KB                       | 937 KB                         |

| Dataset: I                   | mageNet; Model: mcunet-in2 | ; Input Resolution: 160; W  | Vidth Multiplier: N/A; Top-1 | Accuracy: 60.3%                |

| Latency                      | 642 ms                     | 351 ms                      | 280 ms                       | 6463 ms                        |

| Peak Memory                  | 469 KB                     | 238 KB                      | 215 KB                       | 460 KB                         |

| Storage usage                | 1102 KB                    | 849 KB                      | 830 KB                       | 1084 KB                        |

| Dataset: I                   | mageNet; Model: mcunet-in3 | ; Input Resolution: 176; W  | Vidth Multiplier: N/A; Top-1 | Accuracy: 61.8%                |

| Latency                      | 770 ms                     | 414 ms                      | 336 ms                       | 7821 ms                        |

| Peak Memory                  | 493 KB                     | 243 KB                      | 260 KB                       | 493 KB                         |

| Storage usage                | 1106 KB                    | 867 KB                      | 835 KB                       | 1091 KB                        |

| 0 0 1                        | mageNet: Model: mcunet-in4 | · Input Resolution · 160· W | Vidth Multiplier: N/A; Top-1 | Accuracy: 68.0%                |

|                              | OOM                        | 516 ms                      | 463 ms                       | OOM                            |

| Latency<br>Peak Memory       | OOM                        | 342 KB                      | 403 ms<br>416 KB             | OOM                            |

| Storage usage                | OOM                        | 1843 KB                     | 1825 KB                      | OOM                            |

|                              |                            | I                           | Width Multiplier: 0.3; Top-1 |                                |

|                              | 54 ms                      | 35 ms                       | 23 ms                        | 512 ms                         |

| Peak Memory                  | 136 KB                     | 97 KB                       | 35 KB                        | 128 KB                         |

| Storage usage                | 1084 KB                    | 865 KB                      | 777 KB                       | 1065 KB                        |

| 11                           |                            | I                           |                              |                                |

| Dataset: In                  |                            |                             | Width Multiplier: 0.3; Top-2 | <b>Accuracy</b> : 56.2%        |

| Latency                      | 380 ms                     | 205 ms                      | 176 ms                       | 3801 ms                        |

|                              | 453 KB                     | 221 KB                      | 259 KB                       | 453 KB                         |

| Peak Memory                  |                            |                             |                              |                                |

| Peak Memory<br>Storage usage | 1084 KB                    | 865 KB                      | 779 KB                       | 1065 KB                        |

TABLE III. Performance comparison of various tiny models and inference frameworks on STM32H743, which runs at 480MHz with the resource constraint of 512 KB peak memory and 2 MB storage.

<sup>1</sup>All the inference frameworks used in this measurement are the latest versions as of Dec. 19, 2022. <sup>2</sup>The measurement of X-Cube-AI (v7.3.0) is with the default compilation setting, *i.e.*, balanced optimization. <sup>3</sup>OOM denotes Out Of Memory. <sup>4</sup>All the models are available on:https://github.com/mit-han-lab/mcunet.

29 ms

88 KB

768 KB

These frameworks cannot accommodate IoT devices and MCUs with limited memory.

43 ms

173 KB

959 KB

Latency

**Peak Memory**

Storage usage

CMSIS-NN implements optimized kernels to increase inference speed, minimize memory footprint, and enhance the energy

467 ms

173 KB

940 KB

23 ms

61 KB

690 KB

efficiency of deep learning models on ARM Cortex-M processors [41]. X-Cube-AI, designed by STMicroelectronics, enables the automatic conversion of pre-trained deep learning models to run on STM MCUs with optimized kernel libraries [42]. TVM [93] and AutoTVM [99] also supports microcontrollers (referred to as  $\mu$ TVM/microTVM [43]). Compilation techniques can also be employed to reduce memory requirements. For instance, Stoutchinin et al. propose to improve deep learning performance on MCU by optimizing the convolution loop nest [100]. Liberis et al. and Ahn et al. present to reorder the operator executions to minimize peak memory [44, 101], whereas Miao et al. seek to achieve better memory utilization by temporarily swapping data off SRAM [102]. With a similar goal of reducing peak memory, other researchers further propose computing partial spatial regions across multiple layers [103, 104, 105]. Additionally, CMix-NN supports mixedprecision kernel libraries of quantized activation and weight on MCU to reduce memory footprint [46]. TinyEngine, as part of MCUNet, is proposed as a memory-efficient inference engine for expanding the search space and fitting a larger model [8]. TinyEngine transfers the majority of operations from runtime to compile time before generating only the code that will be executed by the TinyNAS model. In addition, TinyEngine adapts memory scheduling to the overall network topology as opposed to layer-by-layer optimization. TensorFlow-Lite Micro (TF-Lite Micro) is among the first deep-learning frameworks to support bare-metal microcontrollers in order to enable deeplearning inference on MCUs with tight memory constraints [47]. However, the aforementioned frameworks only support perlayer inference, which limits the model capacity that can be executed with only a small amount of memory and makes higher-resolution input impossible. Hence, MCUNetV2 proposes a generic patch-by-patch inference scheduling, which operates on a small spatial region of the feature map and drastically reduces peak memory usage, and thus makes the inference with high-resolution input on MCUs feasible [9]. TinyOps combines fast internal memory with an additional slow external memory through Direct Memory Access (DMA) peripheral to enlarge memory size and speed up inference [49]. TinyMaix, similar to CMSIS-NN, is an optimized inference kernel library, but it eschews new but rare features and seeks to preserve the readability and simplicity of the codebase [50].

## B. Recent Progress on TinyML Training

On-device training on small devices is gaining popularity, as it enables machine learning models to be trained and refined directly on small and low-power devices. On-device training offers several benefits, including the provision of personalized services and the protection of user privacy, as user data is never transmitted to the cloud. However, on-device training presents additional challenges compared to on-device inference, due to larger memory footprints and increased computing operations needed to store intermediate activations and gradients.

Researchers have been investigating ways to reduce the memory footprint of training deep learning models. One kind of approach is to design lightweight network structures manually or by utilizing NAS [85, 106, 107]. Another common approach is to trade computation for memory efficiency, such as freeing 6

up activation during inference and recomputing discarded activation during the backward propagation [108, 109]. However, such an approach comes at the expense of increased computation time, which is not affordable for tiny devices with limited computation resources. Another approach is layerwise training, which can also reduce the memory footprint compared to end-to-end training. However, it is not as effective at achieving high levels of accuracy [110]. Another approach reduces the memory footprint by building a dynamic and sparse computation graph for training by activation pruning [111]. Some researchers propose different optimizers [112]. Quantization is also a common approach that reduces the size of activation during training by reducing the bitwidth of training activation [113, 114].

Due to limited data and computational resources, on-device training usually focuses on transfer learning. In transfer learning, a neural network is first pre-trained on a large-scale dataset, such as ImageNet [115], and used as a feature extractor [116, 117, 118]. Then, only the last layer needs to be finetuned on a smaller, task-specific dataset [119, 120, 121, 122]. This approach reduces the memory footprint by eliminating the need to store intermediate activations during training, but due to the limited capacity, the accuracy can be poor when the domain shift is large [52]. Fine-tuning all layers can achieve better accuracy but requires large memory to store activation, which is not affordable for tiny devices [117, 116]. Recently, several memory-friendly on-device training frameworks were proposed [123, 124, 125], but these frameworks targeted larger edge devices (i.e., mobile devices) and cannot be adopted on MCUs. An alternative approach is only updating the parameters of batch normalization layers [126, 127]. This reduces the number of trainable parameters, which however does not translate to memory efficiency [52] because the intermediate activation of batch normalization layers still needs to be stored in the memory.

It has been shown that the activation of a neural network is the main factor limiting the ability to train on small devices. Tiny-Transfer-Learning (TinyTL) addresses this issue by freezing the weights of the network and only fine-tuning the biases, which allows intermediate activations to be discarded during backward propagation, reducing peak memory usage [52]. TinyOL trains only the weights of the final layer, allowing for weight training while keeping the activation small enough to fit on small devices [53]. This enables incremental ondevice streaming of data for training. However, fine-tuning only the biases or the last layer may not provide sufficient precision. To train more layers on devices with limited memory, POET (Private Optimal Energy Training) [54] introduces two techniques: rematerialization, which frees up activations early at the cost of recomputation, and paging, which allows activations to be transferred to secondary storage. POET uses an integer linear program to find the energy-optimal schedule for ondevice training. To further reduce the memory required to store trained weights, MiniLearn applies quantization and dequantization techniques to store the weights and intermediate output in integer precision and dequantizes them to floatingpoint precision during training [55]. When deployed on tiny devices, deep learning models are often quantized to reduce

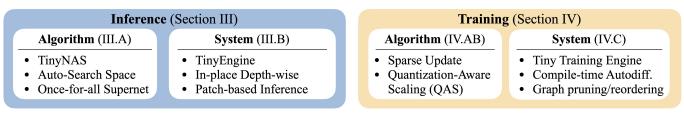

# **TinyML Techniques**

**Fig. 3.** Techniques specifically designed for tiny devices. In order to fully leverage the limited available resources, we need to take careful consideration of both the system and the algorithm. The co-design approach not only enables practical AI applications on a wide range of IoT platforms (*inference*), but also allows AI to continuously learn over time, adapting to a world that is changing fast (*training*).

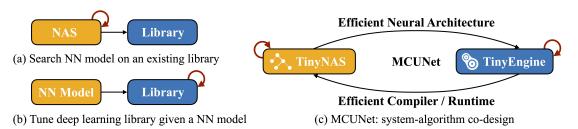

**Fig. 4.** MCUNet jointly designs the neural architecture and the inference scheduling to fit the tight memory resource on microcontrollers. TinyEngine makes full use of the limited resources on MCU, allowing a larger design space for architecture search. With a larger degree of design freedom, TinyNAS is more likely to find a high accuracy model compared to using existing frameworks.

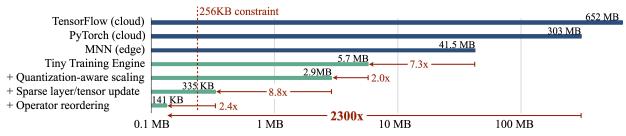

the memory usage of parameters and activations. However, even after quantization, the parameters may still be too large to fit in the limited hardware resources, preventing full backpropagation. To address these challenges, MCUNetV3 proposes an algorithm-system co-design approach [56]. The algorithm part includes Quantization-Aware Scaling (QAS) and the sparse update. QAS calibrates the gradient scales and stabilizes 8-bit quantized training, while the sparse update skips the gradient computation of less important layers and sub-tensors. The system part includes the Tiny Training Engine (TTE), which has been developed to support both QAS and the sparse update, enabling on-device learning on microcontrollers with limited memory, such as those with 256KB or even less.

## **III. TINY INFERENCE**

In this section, we discuss our recent work, MCUNet family [8, 9], a system-algorithm co-design framework that jointly optimizes the NN architecture (TinyNAS) and the inference scheduling (TinyEngine) in the same loop (Figure 4). Compared to traditional methods that either (a) optimize the neural network using neural architecture search based on a given deep learning library (*e.g.*, TensorFlow, PyTorch) [86, 85, 87], or (b) tune the library to maximize the inference speed for a given network [93, 99], MCUNet can better utilize the resources by system-algorithm co-design, enabling a better performance on microcontrollers. The design space of the inference part is listed in Figure 3 (left).

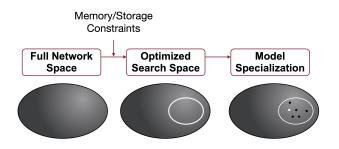

# A. TinyNAS: Automated Tiny Model Design

TinyNAS is a two-stage neural architecture search method that first optimizes the search space to fit the tiny and diverse resource constraints, and then performs neural architecture search within the optimized space. By optimizing the search space, it significantly improves the accuracy of the final model.

## 1) Automated search space optimization.

TinyNAS proposes to optimize the search space automatically at *low cost* by analyzing the computation distribution of the satisfying models. To fit the tiny and diverse resource constraints of different microcontrollers, TinyNAS scales the *input resolution* and the *width multiplier* of the mobile search space [86]. It chooses from an input resolution spanning  $R = \{48, 64, 80, ..., 192, 208, 224\}$  and a width multiplier  $W = \{0.2, 0.3, 0.4, ..., 10\}$  to cover a wide spectrum of resource constraints. This leads to  $12 \times 9 = 108$  possible search space configurations  $S = W \times R$ . Each search space configuration contains  $3.3 \times 10^{25}$  possible sub-networks. The goal is to find the best search space configuration  $S^*$  that contains the model with the highest accuracy while satisfying the resource constraints.

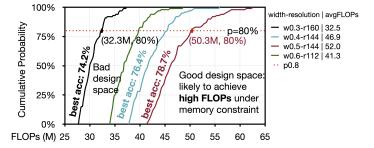

Finding  $S^*$  is non-trivial. One way is to perform neural architecture search on each of the search spaces and compare the final results. But the computation would be astronomical. Instead, TinyNAS evaluates the quality of the search space by randomly sampling *m* networks from the search space and comparing the distribution of satisfying networks. Instead of collecting the Cumulative Distribution Function (CDF) of each satisfying network's *accuracy* [88], which is computationally heavy due to tremendous training, it only collects the CDF of *FLOPs* (see Figure 5(b)). The intuition is that, within the same model family, the accuracy is usually positively related to the computation [128, 61]. A model with larger computation has a larger capacity, which is more likely to achieve higher accuracy.

(a) TinyNAS: two-stage neural architecture search

(b) Search space optimization by analyzing FLOPs CDF

**Fig. 5.** (a) TinyNAS is a two-stage neural architecture search method. It first specifies a sub-space according to the constraints, and then performs model specialization. (b) TinyNAS selects the best search space by analyzing the FLOPs CDF of different search spaces. Each curve represents a design space. Our insight is that the design space that is more likely to produce *high FLOPs* models under the memory constraint gives higher model capacity, thus more likely to achieve high accuracy.

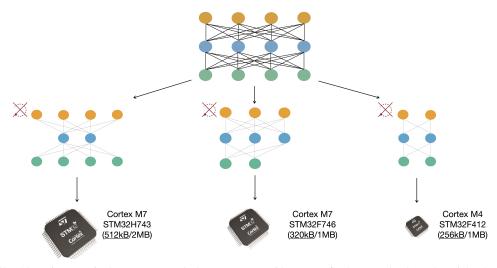

Fig. 6. Once-For-All [129] trains one single super network that supports a wide range of sub-networks through weight sharing, and specializes different sub-network architectures for different MCU hardware.

Take the study of the best search space for ImageNet-100 (a 100-class classification task taken from the original ImageNet) on STM32F746 as an example. We show the FLOPs distribution CDF of the top-10 search space configurations in Figure 5(b). Only the models that satisfy the memory requirement at the best scheduling from TinyEngine are kept. For example, according to the experimental results on ImageNet-100, using the solid red space (average FLOPs 52.0M) achieves 2.3% better accuracy compared to using the solid green space (average FLOPs 46.9M), showing the effectiveness of automated search space optimization.

# 2) Resource-constrained model specialization with Once-For-All NAS.

To specialize network architecture for various microcontrollers, we need to keep a low neural architecture search cost. Given an optimized search space, TinyNAS further performs one-shot neural architecture search [130, 131] to efficiently find a good model. Specifically, it follows Once-For-All (OFA) NAS [129] to perform network specialization (Figure 6). We train one super network that contains all the possible subnetworks through *weight sharing* and use it to estimate the performance of each sub-network. The search space is based on the widely-used mobile search space [86, 85, 87, 129] and supports variable kernel sizes for depth-wise convolution (3/5/7), variable expansion ratios for inverted bottleneck (3/4/6) and variable stage depths (2/3/4). The number of possible subnetworks that TinyNAS can cover in the search space is large:  $2 \times 10^{19}$ . For each batch of data, it randomly samples 4 subnetworks, calculates the loss, backpropagates the gradients for each sub-network, and updates the corresponding weights. It then performs an evolution search to find the best model within the search space that meets the onboard resource constraints while achieving the highest accuracy. For each sampled network, it uses TinyEngine to optimize the memory scheduling to measure the optimal memory usage. With such a kind of codesign, we can efficiently fit the tiny memory budget.

## B. TinyEngine: A Memory-Efficient Inference Library

Researchers used to assume that using different deep learning frameworks (libraries) will only affect the *inference speed* but not the *accuracy*. However, this is not the case for TinyML: the efficiency of the inference library matters a lot to both the latency and accuracy of the searched model. Specifically, a good inference framework will make full use of the limited resources in MCUs, avoiding waste of memory, and allowing

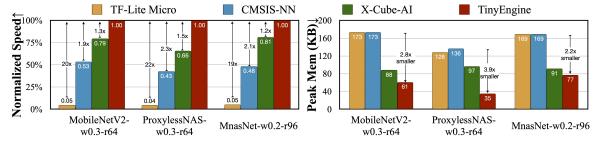

Fig. 7. TinyEngine achieves higher inference efficiency than existing inference frameworks while reducing memory usage. Left: TinyEngine is up to  $22 \times$ ,  $2.3 \times$ , and  $1.5 \times$  faster than TF-Lite Micro, CMSIS-NN, and X-Cube-AI, respectively. **Right**: By reducing the memory usage, TinyEngine can run various model designs with tiny memory, enlarging the design space for TinyNAS under the limited memory of MCU.

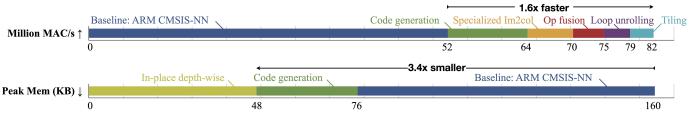

Fig. 8. TinyEngine outperforms existing libraries by eliminating runtime overheads, specializing each optimization technique, and adopting in-place depth-wise convolution. This effectively enlarges design space for TinyNAS under a given latency/memory constraint.

a larger search space for architecture search. With a larger degree of design freedom, TinyNAS is more likely to find a high-accuracy model. Thus, TinyNAS is co-designed with a memory-efficient inference library, TinyEngine.

# 1) Code generation.

Most existing inference libraries (e.g., TF-Lite Micro, CMSIS-NN) are interpreter-based. Though it is easy to support cross-platform development, it requires extra memory, the most expensive resource in MCU, to store the meta-information (such as model structure parameters). Instead, TinyEngine only focuses on MCU devices and adopts code generatorbased compilation. This not only avoids the time for runtime interpretation, but also frees up the memory usage to allow design and inference of larger models. Compared to CMSIS-NN, TinyEngine reduced memory usage by  $2.1 \times$  and improve inference efficiency by 22% via code generation, as shown in Figures 7 and 8.

The binary size of TinyEngine is lightweight, making it very memory- TF-Lite Micro CMSIS-NN efficient for MCUs. The model directly compiled by well-known pro- a gramming languages for deep learning (e.g., Python, Cython, etc.) cannot be run on MCUs as the size of their dependencies and packages are already larger than the Flash size of MCUs, let alone the size of the compiled model. Besides, unlike interpreter-based TF-Lite Micro,

which prepares the code for every operation (e.g., conv, softmax) to support cross-model inference even if they are not used, which has high redundancy. TinyEngine only compiles the operations that are used by a given model into the binary. That is, the reduction of binary size of the model

compiled by TinyEngine comes from not only the benefit of compilation over interpretation but also the model-specific optimization/specialization. As shown in Figure 9, such modeladaptive compilation reduces code size by up to  $4.5 \times$  and  $5.0 \times$ compared to TF-Lite Micro and CMSIS-NN, respectively.

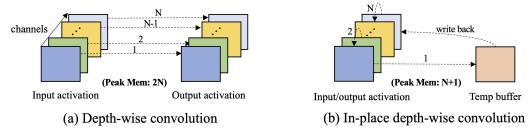

# 2) In-place depth-wise convolution

TinyEngine supports *in-place* depth-wise convolution to further reduce peak memory. Different from standard convolutions, depth-wise convolutions do not perform filtering across channels. Therefore, once the computation of a channel is completed, the input activation of the channel can be overwritten and used to store the output activation of another channel, allowing activation of depth-wise convolutions to be updated in-place as shown in Figure 10. This method reduces the measured memory usage by  $1.6 \times$  as shown in Figure 8.

# 3) Patched-based Inference

TinyNAS and TinyEngine have significantly reduced the peak memory at the same level of accuracy. But we still notice a very imbalanced peak memory usage per block.

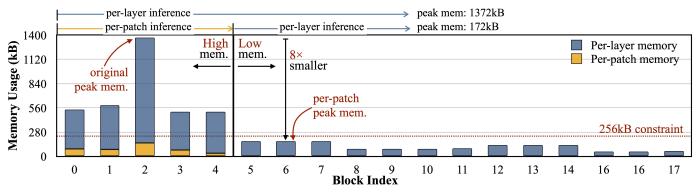

Imbalanced memory distribution. As an example, the perblock peak memory usage of MobileNetV2 [4] is shown in Figure 11. The profiling is done in int8. There is a clear pattern of imbalanced memory usage distribution. The first 5 blocks have large peak memory, exceeding the memory constraints of MCUs, while the remaining 13 blocks easily fit 256KB memory constraints. The third block has 8× larger memory usage than the rest of the network, becoming the memory bottleneck. There are similar patterns for other efficient network designs, which is quite common across different CNN backbones, even for models specialized for memory-limited microcontrollers [8].

The phenomenon applies to most single-branch or residual

**Fig. 10.** TinyEngine reduces peak memory by performing in-place depth-wise convolution. **Left:** Conventional depth-wise convolution requires 2N memory footprint for activations. **Right:** in-place depth-wise convolution reduces the memory of depth-wise convolutions to N+1. Specifically, the output activation of the first channel is stored in a temporary buffer. Then, for each following channel, the output activation overwrites the input activation of its previous channel. Finally, the output activation of the first channel is stored in the buffer is written back to the input activation of the last channel.

**Fig. 11.** MobileNetV2 [4] has a very *imbalanced memory usage distribution*. The peak memory is determined by the first 5 blocks with high peak memory, while the later blocks all share a small memory usage. By using per-patch inference ( $4 \times 4$  patches), we are able to significantly reduce the memory usage of the first 5 blocks, and reduce the overall peak memory by  $8 \times$ , fitting MCUs with a 256kB memory budget. Notice that the model architecture and accuracy are not changed for the two settings. The memory usage is measured in int8.

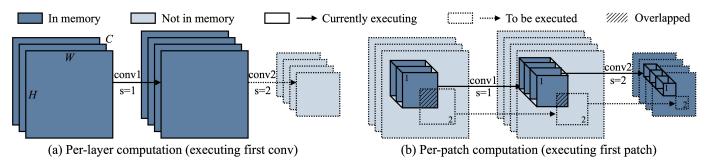

**Fig. 12.** Per-patch inference can significantly reduce the peak memory required to execute a sequence of convolutional layers. We study two convolutional layers (stride 1 and 2). Under per-layer computation (a), the first convolution has a large input/output activation size, dominating the peak memory requirement. With per-patch computation (b), we allocate the buffer to host the final output activation, and compute the results *patch-by-patch*. We only need to store the activation from *one patch* but not the entire feature map, reducing the peak memory (the first input is the image, which can be partially decoded from a compressed format like JPEG).

CNN designs due to the hierarchical structure<sup>\*</sup>: after each stage, the image resolution is down-sampled by half, leading to  $4\times$  fewer pixels, while the channel number increases only by  $2\times$  [132, 10, 5] or by an even smaller ratio [4, 133, 106], resulting in a decreasing activation size. Therefore, the memory bottleneck tends to appear at the early stage of the network, after which the peak memory usage is much smaller.

Breaking the Memory Bottleneck with Patch-based Inference. TinEngine breaks the memory bottleneck of the initial layers with *patch-based inference* (Figure 12). Existing deep learning inference frameworks (*e.g.*, TensorFlow Lite Micro [90], TinyEngine [8], microTVM [93], *etc.*) use a *layer-by-layer* execution. For each convolutional layer, the inference library first allocates the input and output activation buffer in SRAM, and releases the input buffer after the *whole* layer computation is finished. The patch-based inference runs the initial memory-intensive stage in a *patch-by-patch* manner. For each time, it only runs the model on a small spatial region (>10× smaller than the whole area), which effectively cuts down the peak memory usage. After this stage is finished, the rest of the network with a small peak memory is executed in a

<sup>\*</sup>some CNN designs have highly complicated branching structure (*e.g.*, NASNet [83]), but they are generally less efficient for inference [6, 86, 85]; thus not widely used for edge computing.

Fig. 13. The redistributed MobileNetV2 (MbV2-RD) has reduced receptive field for the per-patch inference stage and increased receptive field for the per-layer stage. The two networks have the same level of performance, but MbV2-RD has a smaller overhead under patch-based inference. The mobile inverted block is denoted as MB{expansion ratio} {kernel size}. The dashed border means stride=2.

normal layer-by-layer manner (upper notations in Figure 11).

An example of two convolutional layers (with stride 1 and 2) is shown in Figure 12. For conventional per-layer computation, the first convolutional layer has large input and output activation size, leading to a high peak memory. With spatial partial computation, it allocates the buffer for the final output and computes its values *patch-by-patch*. In this manner, it only needs to store the activation from *one patch* instead of the *whole feature map*.

**Reducing Computation Overhead by Redistributing the** Receptive Field. The significant memory saving comes at the cost of computation overhead. To maintain the same output results as per-layer inference, the non-overlapping output patches correspond to overlapping patches in the input image (the shadow area in Figure 12(b)). This is because convolutional filters with kernel size >1 contribute to increasing receptive fields. The computation overhead is related to the receptive field of the patch-based initial stage. Consider the output of the patch-based stage, the larger receptive field it has on the input image, the larger resolution for each patch, leading to a larger overlapping area and repeated computation. There are some focusing on addressing the issue from the hardware perspective [103]. However, since such practices may not be general to all devices, TinyEngine solves the problem from the network architecture side.

MCUNet proposes to *redistribute* the receptive field (RF) of the CNN to reduce computation overhead. The basic idea is: (1) reduce the receptive field of the patch-based initial stage; (2) increase the receptive field of the later stage. Reducing RF for the initial stage helps to reduce the size of each input patch and repeated computation. However, some tasks may have degraded performance if the overall RF is smaller (*e.g.*, detecting large objects). Therefore, it further increases the RF of the later stage to compensate for the performance loss. A manually tuned example of MobileNetV2 is shown in Figure 13. After redistributing the receptive field ("MbV2-RD"), the computation overhead is negligible.

MCUNet automates the process with joint search (introduced in the next section).

# C. Co-Design: Joint Neural Architecture and Inference Scheduling Search

## 1) Co-Design Loop

The optimization algorithms for model architectures and inference engines are tightly coupled. For example, redistributing the receptive field allows us to enjoy the benefit of memory reduction at minimal computation/latency overhead, which allows larger freedom when designing the backbone architecture (e.g., we can now use a larger input resolution). To explore such a large design space, MCUNet jointly optimizes the neural architecture and the inference scheduling in an automated manner. Given a certain dataset and hardware constraints (SRAM limit, Flash limit, latency limit, etc.), our goal is to achieve the highest accuracy while satisfying all the constraints. For the model optimization, it uses NAS to find a good candidate network architecture; for the scheduling optimization, it optimizes the knobs like the patches number pand the number of blocks n to perform patch-based inference, and other knobs in TinyEngine [8].

There are some trade-offs during the co-design. For example, given the same constraints, it can choose to use a smaller model that fits per-layer execution (p = 1, no computation overhead), or a larger model and per-patch inference (p > 1, with a small computation overhead). Therefore, MCUNet puts both sides in the same loop and uses evolutionary search to find the best set of ( $k_{[]}, e_{[]}, d_{[]}, w_{[]}, r, p, n$ ) satisfying constraints. Therefore, The two dimensions are jointly searched in the same loop with evolutionary search.

# 2) Experimental Results

## a) Pushing the ImageNet record on MCUs.

With joint optimization of neural architecture and inference scheduling, MCUNet significantly pushes the state-of-the-art results for MCU-based tiny image classification.

We compared MCUNet with existing state-of-the-art solutions on ImageNet classification under two hardware settings: 256kB SRAM/1MB Flash and 512kB SRAM/2MB Flash. The former represents a widely used Cortex-M4 microcontroller; the latter corresponds to a higher-end Cortex-M7. The goal is to achieve the highest ImageNet accuracy on resource-constrained MCUs (Table IV). MCUNet significantly improves the ImageNet accuracy of tiny deep learning on microcontrollers. Under

**TABLE IV.** MCUNet significantly improves the ImageNet accuracy on microcontrollers, outperforming the state-of-the-arts by **4.6%** under 256kB SRAM and **3.3%** under 512kB. Lower or mixed precisions (marked gray) are orthogonal techniques, which we leave for future work. Out-of-memory (OOM) results are struck-out.

| Model / Library                                                                                                                             | Quant.                | MACs                 | SRAM                                 | Flash                    | Top-1                   | Top-5                               |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--------------------------------------|--------------------------|-------------------------|-------------------------------------|

| STM32F412 (2                                                                                                                                | 256kB SRA             | M, 1MB               | Flash)                               |                          |                         |                                     |

| MbV2 $0.35 \times (r=144)$ [4] / TinyEngine [8]<br>Proxyless $0.3 \times (r=176)$ [85] / TinyEngine [8]                                     | int8<br>int8          | 24M<br>38M           | <del>308kB</del><br><del>292kB</del> | 862kB<br>892kB           | 49.0%<br>56.2%          | 73.8%<br>79.7%                      |

| MbV1 $0.5 \times (r=192)$ [5] / Rusci <i>et al.</i> [45]<br>MCUNet (TinyNAS / TinyEngine) [8]<br>MCUNet (TinyNAS / TinyEngine) [8]          | mixed<br>int8<br>int4 | 110M<br>68M<br>134M  | <256kB<br>238kB<br>233kB             | <1MB<br>1007kB<br>1008kB | 60.2%<br>60.3%<br>62.0% | -                                   |

| MCUNet-M4 (w/ patch)                                                                                                                        | int8                  | 119M                 | 196kB                                | 1010kB                   | 64.9%                   | 86.2%                               |

| STM32H743 (5                                                                                                                                | 512kB SRA             | M, 2MB               | Flash)                               |                          |                         |                                     |

| MbV1 0.75× ( <i>r</i> =224) [5] / Rusci <i>et al.</i> [45]<br><b>MCUNet (TinyNAS / TinyEngine) [8]</b><br>MCUNet (TinyNAS / TinyEngine) [8] | mixed<br>int8<br>int4 | 317M<br>126M<br>474M | <512kB<br>452kB<br>498kB             | <2MB<br>2014kB<br>2000kB | 68.0%<br>68.5%<br>70.7% | -                                   |

| MCUNet-H7 (w/ patch)                                                                                                                        | int8                  | 256M                 | 465kB                                | 2032kB                   | 71.8%                   | 90.7%                               |

|                                                                                                                                             |                       |                      |                                      |                          |                         |                                     |

| MCUNet (w/ patch) MCUNet (<br>62kB 118kB 256kB 256kB constraint<br>0 30kB 0 MCUNet (                                                        | 92 90 88              |                      | MbV2+TF-<br>+4.6%                    |                          | Proxyles:               | s+TF-Lite                           |

| $\begin{array}{c} 62kB \\ 2 \\ - \\ - \\ - \\ - \\ - \\ - \\ - \\ - \\ -$                                                                   | 92                    |                      |                                      |                          | faster                  | s+TF-Lite<br>M < 320k<br>Ylash < 1M |

Fig. 14. Left: MCUNet has better visual wake word (VWW) accuracy vs. peak SRAM trade-off. Compared to MCUNet [8], MCUNet achieves better accuracy at  $4.0 \times$  smaller peak memory. It achieves >90% accuracy under <32kB memory, facilitating deployment on extremely small hardware. **Right**: patch-based method expands the search space that can fit the MCU, allowing better accuracy vs. latency trade-off.

256kB SRAM/1MB Flash, MCUNet outperforms the state-ofthe-art method [8] by 4.6% at 18% lower peak SRAM. Under 512kB SRAM/2MB Flash, MCUNet achieves a new *record* ImageNet accuracy of 71.8% on commercial microcontrollers, which is 3.3% compared to the best solution under the same quantization policy. Lower-bit (int4) or mixed-precision quantization can further improve the accuracy (marked in gray in the table).

# b) Visual Wake Words under 32kKB SRAM.

Visual wake word (VWW) reflects the low-energy application of TinyML. MCUNet allows running a VWW model with a modest memory requirement. As in Figure 14<sup>†</sup>, MCUNet outperforms state-of-the-art method [8] for both accuracy vs. peak memory and accuracy vs. latency trade-off. Compared to per-layer inference, MCUNet can achieve better accuracy using 4.0× smaller memory. Actually, it can achieve >90% accuracy under 32kB SRAM requirement, allowing model deployment on low-end MCUs like STM32F410 costing only \$1.6. Per-patch inference also expands the search space, giving us more freedom to find models with better accuracy vs. latency trade-off.

# c) MCU-based detection on Pascal VOC.

Object detection is sensitive to a smaller input resolution [9]. Current state-of-the-art [8] cannot achieve a decent detection performance on MCUs due to the resolution bottleneck. MCUNet breaks the memory bottleneck for detectors and improves the mAP by double digits.

The object detection results on Pascal VOC trained with YOLOv3 [135] are shown in Table V, including results for M4 MCU with 256kB SRAM and H7 MCU with 512kB SRAM. On H7 MCU, MCUNet-H7 improves the mAP by 16.7% compared to the state-of-the-art method MCUNet [8]. It can also scale down to fit a cheaper commodity Cortex-M4 MCU with only 256kB SRAM, while still improving the mAP by 13.2% at  $1.9 \times$  smaller peak SRAM. Note that MCUNet-M4 shares a similar computation with MCUNet (172M *vs.* 168M) but a much better mAP. This is because the expanded search space from patch-based inference allows us to choose a better configuration of larger input resolution and smaller models.

# d) Memory-efficient face detection.

The performance of MCUNet for memory-efficient face detection on WIDER FACE [136] dataset are shown in Table VI. The analytic memory usage of the detector backbone in fp32 is reported following [105]. The models are trained with S3FD

<sup>&</sup>lt;sup>†</sup>Note that MCUNetV2 refers to the version w/ patch-based inference, while MCUNet refers to per-layer inference.

**TABLE V.** MCUNet significantly improves Pascal VOC [134] object detection on MCU by allowing a higher input resolution. Under STM32H743 MCU constraints, MCUNet-H7 improves the mAP by 16.9% compared to [8], achieving a record performance on MCU. It can also scale down to cheaper MCU STM32F412 with only 256kB SRAM while still improving mAP by 13.2% at  $1.9 \times$  smaller peak SRAM and a similar computation.

| MCU Model   | Constraint     | Model                        | #Param         | MACs        | peak SRAM                 | VOC mAP        | Gain   |

|-------------|----------------|------------------------------|----------------|-------------|---------------------------|----------------|--------|

| H743 (~\$7) | SRAM<br><512kB | MbV2+CMSIS [8]<br>MCUNet [8] | 0.87M<br>1.20M | 34M<br>168M | <del>519kB</del><br>466kB | 31.6%<br>51.4% | 0%     |

|             |                | MCUNet-H7                    | 0.67M          | 343M        | 438kB                     | 68.3%          | +16.9% |

| F412 (~\$4) | <256kB         | MCUNet-M4                    | 0.47M          | 172M        | 247kB                     | 64.6%          | +13.2% |

**TABLE VI.** MCUNet outperforms existing methods for memory-efficient face detection on WIDER FACE [136] dataset. Compared to RNNPool-Face-C [105], MCUNet-L can achieve similar mAP at  $3.4 \times$  smaller peak SRAM and  $1.6 \times$  smaller computation. The model statistics are profiled on  $640 \times 480$  RGB input images following [105].

| Method                                           | MACs ↓ Peak Memory ↓    |                                                 |                             | mAP $\uparrow$       |                             | mAP ( $\leq$ 3 faces) $\uparrow$ |                             |                             |

|--------------------------------------------------|-------------------------|-------------------------------------------------|-----------------------------|----------------------|-----------------------------|----------------------------------|-----------------------------|-----------------------------|

|                                                  |                         | (fp32)                                          | Easy                        | Medium               | Hard                        | Easy                             | Medium                      | Hard                        |

| EXTD [137]<br>LFFD [138]<br>RNNPool-Face-C [105] | 8.49G<br>9.25G<br>1.80G | 18.8MB (9.9×)<br>18.8MB (9.9×)<br>6.44MB (3.4×) | 0.90<br>0.91<br><b>0.92</b> | 0.88<br>0.88<br>0.89 | 0.82<br>0.77<br><b>0.70</b> | 0.93<br>0.83<br><b>0.95</b>      | 0.93<br>0.83<br><b>0.94</b> | 0.91<br>0.82<br><b>0.92</b> |

| MCUNet-L                                         | 1.10G                   | <b>1.89MB</b> (1.0×)                            | 0.92                        | 0.90                 | 0.70                        | 0.94                             | 0.93                        | 0.92                        |

| EagleEye [139]<br>RNNPool-Face-A [105]           | <b>0.08G</b><br>0.10G   | 1.17MB (1.8×)<br>1.17MB (1.8×)                  | 0.74<br>0.77                | 0.70<br>0.75         | 0.44<br>0.53                | 0.79<br>0.81                     | 0.78<br>0.79                | 0.75<br>0.77                |

| MCUNet-S                                         | 0.11G                   | <b>672kB</b> (1.0×)                             | 0.85                        | 0.81                 | 0.55                        | 0.90                             | 0.89                        | 0.87                        |

face detector [140] following [105] for a fair comparison. The reported mAP is calculated on samples with  $\leq$  3 faces, which is a more realistic setting for tiny devices. MCUNet outperforms existing solutions under different scales. MCUNet-L achieves comparable performance at 3.4× smaller peak memory compared to RNNPool-Face-C [8] and 9.9× smaller peak memory compared to LFFD [138]. The computation is also 1.6× and 8.4× smaller. MCUNet-S consistently outperforms RNNPool-Face-A [105] and EagleEye [139] at 1.8× smaller peak memory.

# IV. TINY TRAINING

In addition to inference, tiny on-device training is a growing direction that allows us to *adapt* the pre-trained model to newly collected sensory data *after* deployment. By training and adapting *locally* on the edge, the model can learn to continuously improve its predictions and perform lifelong learning and user customization. By bringing training closer to the sensors, it also helps to protect user privacy when handling sensitive data (*e.g.*, healthcare).

However, on-device training on tiny edge devices is extremely challenging and fundamentally different from cloud training. Tiny IoT devices (*e.g.*, microcontrollers) typically have a limited SRAM size like 256KB. Such a small memory budget is hardly enough for the *inference* of deep learning models [8, 9, 48, 141, 142, 143, 44, 45], let alone the *training*, which requires extra computation for the backward and extra memory for intermediate activation [109]. On the other hand, modern deep training frameworks (*e.g.*, PyTorch [89], TensorFlow [144]) are usually designed for cloud servers and require a large memory footprint (>300MB) even when training a small model (*e.g.*, MobileNetV2-w0.35 [4]) with batch size 1. The huge gap (>1000×) makes it impossible to run on tiny IoT devices. Furthermore, devices like microcontrollers are baremetal and do not have an operational system and the runtime support needed by existing training frameworks. Therefore, we need to jointly design the *algorithm* and the *system* to enable tiny on-device training.

Deep learning training systems such as PyTorch [89], TensorFlow [144], JAX [92], MXNet [91], *etc.* do not consider the tight resources on edge devices. Edge deep learning inference frameworks like TVM [93], TF-Lite [94], NCNN [97], *etc.* provide a slim runtime, but lack the support for backpropagation. There are low-cost efficient transfer learning algorithms like training only the final classifier layer, biasonly update [52], *etc.* However, the existing training systems can not realize the theoretical saving into measured savings. The downstream accuracy of such update schemes is also low (Figure 18). There is a need for training systems that can effectively utilize the limited resources on edge devices."

In order to bridge the gap and enable tiny on-device training with algorithm-system co-design, there are two unique challenges in tiny on-device training: (1) the model is quantized on edge devices. A *real* quantized graph is difficult to optimize due to mixed-precision tensors and the lack of Batch Normalization layers [145]; (2) the limited hardware resource (memory and computation) of tiny hardware does not allow full back-propagation, as the memory usage can easily exceed the SRAM of microcontrollers by more than an order of magnitude. To cope with the difficulties, TinyTraining proposes the following designs

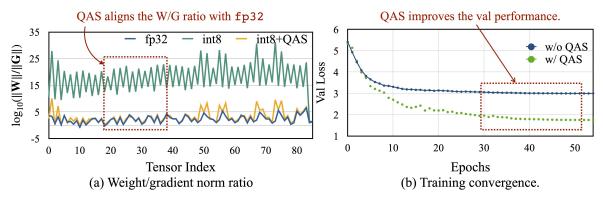

# A. Quantization Aware Scaling

Neural networks usually need to be quantized to fit the limited memory of edge devices [8, 146]. For a fp32 linear layer  $\mathbf{y}_{\text{fp32}} = \mathbf{W}_{\text{fp32}}\mathbf{x}_{\text{fp32}} + \mathbf{b}_{\text{fp32}}$ , the int8 quantized

Fig. 15. Algorithm and system co-design reduces the training memory from 303MB (PyTorch) to 149KB with the same transfer learning accuracy, leading to  $2077 \times$  reduction. The numbers are measured with MobilenetV2-w0.35 [4], batch size 1 and resolution  $128 \times 128$ . It can be deployed to a microcontroller with 256KB SRAM.

counterpart is:

$$\bar{\mathbf{y}}_{\text{int8}} = \text{cast2int8}[s_{\text{fp32}} \cdot (\mathbf{W}_{\text{int8}} \bar{\mathbf{x}}_{\text{int8}} + \mathbf{b}_{\text{int32}})], (1)$$

where  $\bar{\cdot}$  denotes the tensor being quantized to fixed-point numbers, and *s* is a floating-point scaling factor to project the results back into int8 range. The gradient update for the weights can be presented as:  $\bar{\mathbf{W}}'_{\text{int8}} = \texttt{cast2int8}(\bar{\mathbf{W}}_{\text{int8}} - \alpha \cdot \mathbf{G}_{\bar{\mathbf{W}}})$ , where  $\alpha$  is the learning rate, and  $\mathbf{G}_{\bar{\mathbf{W}}}$  is the gradient of the weights. After applying the gradient update, the weights are rounded back to 8-bit integers.

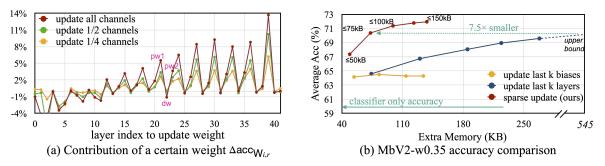

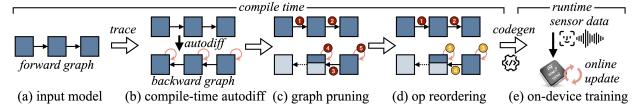

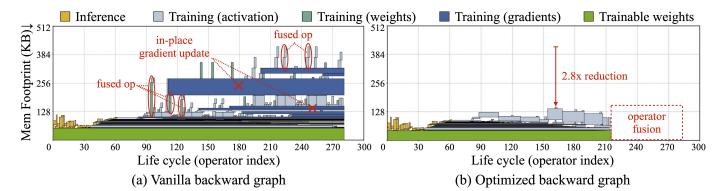

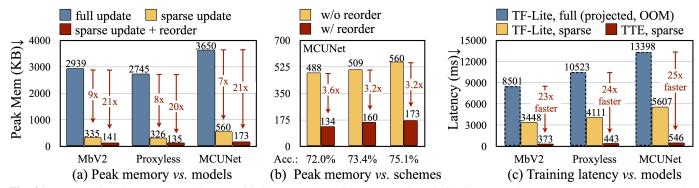

**Gradient Scale Mismatch**: Unlike fine-tuning floating-point model on the cloud, training with *a real* quantized graph<sup>‡</sup> is difficult: the quantized graph has tensors of different bitprecisions (int8, int32, fp32, shown in Equation 1) and lacks Batch Normalization [145] layers (fused), leading to unstable gradient update.